# MIC4421A/4422A

#### 9A Peak Low-Side MOSFET Driver Bipolar/CMOS/DMOS Process

### **General Description**

MIC4421A and MIC4422A MOSFET drivers are rugged, efficient, and easy to use. The MIC4421A is an inverting driver, while the MIC4422A is a non-inverting driver.

Both versions are capable of 9A (peak) output and can drive the largest MOSFETs with an improved safe operating margin. The MIC4421A/4422A accepts any logic input from 2.4V to  $V_S$  without external speed-up capacitors or resistor networks. Proprietary circuits allow the input to swing negative by as much as 5V without damaging the part. Additional circuits protect against damage from electrostatic discharge.

MIC4421A/4422A drivers can replace three or more discrete components, reducing PCB area requirements, simplifying product design, and reducing assembly cost.

Modern Bipolar/CMOS/DMOS construction guarantees freedom from latch-up. The rail-to-rail swing capability of CMOS/DMOS insures adequate gate voltage to the MOSFET during power up/down sequencing. Since these devices are fabricated on a self-aligned process, they have very low crossover current, run cool, use little power, and are easy to drive.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

- High peak-output current: 9A Peak (typ.)

- Wide operating range: 4.5V to 18V (typ.)

- Minimum pulse width: 50ns

- Latch-up proof: fully isolated process is inherently immune to any latch-up

- Input will withstand negative swing of up to 5V

- High capacitive load drive: 47,000pF

- Low delay time: 15ns (typ.)

- Logic high input for any voltage from 2.4V to  $V_{\rm S}$

- Low equivalent input capacitance: 7pF (typ.)

- Low supply current: 500µA (typ.)

- Output voltage swing to within 25mV of GND or  $V_{\rm S}$

### **Applications**

- Switch mode power supplies

- Motor controls

- Pulse transformer driver

- Class-D switching amplifiers

- Line drivers

- Driving MOSFET or IGBT parallel chip modules

- Local power ON/OFF switch

- Pulse generators

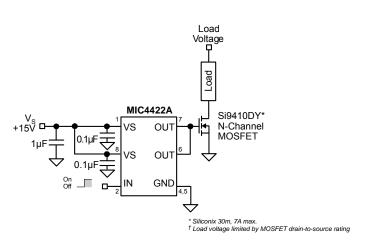

Low-Side Power Switch

# **Ordering Information**

| Part Number |            | Configuration | Temperature Range | Baakaga      |  |

|-------------|------------|---------------|-------------------|--------------|--|

| Standard    | Pb-Free    | Configuration | Temperature Range | Package      |  |

| MIC4421AAM* |            | Inverting     | –55° to +125°C    | 8-Pin SOIC   |  |

| MIC4421ABM  | MIC4421AYM | Inverting     | –40° to +85°C     | 8-Pin SOIC   |  |

| MIC4421ACM  | MIC4421AZM | Inverting     | 0° to +70°C       | 8-Pin SOIC   |  |

| MIC4421ABN  | MIC4421AYN | Inverting     | –40° to +85°C     | 8-Pin PDIP   |  |

| MIC4421ACN  | MIC4421AZN | Inverting     | 0° to +70°C       | 8-Pin PDIP   |  |

| MIC4421ACT  | MIC4421AZT | Inverting     | 0° to +70°C       | 5-Pin TO-220 |  |

| MIC4422AAM* |            | Non-Inverting | –55° to +125°C    | 8-Pin SOIC   |  |

| MIC4422ABM  | MIC4422AYM | Non-Inverting | –40° to +85°C     | 8-Pin SOIC   |  |

| MIC4422ACM  | MIC4422AZM | Non-Inverting | 0° to +70°C       | 8-Pin SOIC   |  |

| MIC4422ABN  | MIC4422AYN | Non-Inverting | –40° to +85°C     | 8-Pin PDIP   |  |

| MIC4422ACN  | MIC4422AZN | Non-Inverting | 0° to +70°C       | 8-Pin PDIP   |  |

| MIC4422ACT  | MIC4422AZT | Non-Inverting | 0° to +70°C       | 5-Pin TO-220 |  |

\* Special order. Contact factory.

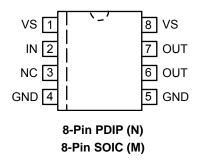

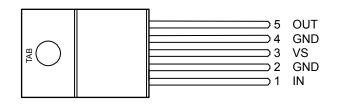

# **Pin Configuration**

5-Pin TO-220 (T)

# **Pin Description**

| Pin Number<br>DIP, SOIC | Pin Number<br>TO-220-5 | Pin Name | Pin Name                                                            |

|-------------------------|------------------------|----------|---------------------------------------------------------------------|

| 2                       | 1                      | IN       | Control Input.                                                      |

| 4, 5                    | 2, 4                   | GND      | Ground: Duplicate pins must be externally connected together.       |

| 1, 8                    | 3, TAB                 | VS       | Supply Input: Duplicate pins must be externally connected together. |

| 6, 7                    | 5                      | OUT      | Output: Duplicate pins must be externally connected together.       |

| 3                       | —                      | NC       | Not connected.                                                      |

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>s</sub> )                                   | +20V             |

|--------------------------------------------------------------------|------------------|

| Control Input Voltage (V <sub>IN</sub> ) V <sub>S</sub> +          | 0.3V to GND – 5V |

| Control Input Current ( $V_{IN} > V_S$ )                           | 50mA             |

| Power Dissipation, $T_A \leq +25^{\circ}C^{(4)}$                   |                  |

| PDIP (θ <sub>JA</sub> )                                            | 1478mW           |

| SOIC (θ <sub>JA</sub> )                                            | 767mW            |

| ΤΟ-220 (θ <sub>JA</sub> )                                          | 1756W            |

| Lead Temperature (soldering, #sec.)                                |                  |

| Storage Temperature (T <sub>s</sub> )                              | –65°C to +150°C  |

| Storage Temperature (T <sub>s</sub> )<br>ESD Rating <sup>(3)</sup> | 2kV              |

|                                                                    |                  |

# **Operating Ratings**<sup>(2)</sup>

| Supply Voltage ( $V_S$ )                  | +4.5V to +18V   |

|-------------------------------------------|-----------------|

| Ambient Temperature (T <sub>A</sub> )     |                 |

| A Version                                 | –55°C to +125°C |

| B Version                                 | –40°C to +85°C  |

| C Version                                 | 0°C to +70°C    |

| Junction Temperature (T <sub>J</sub> )    | 150°C           |

| Package Thermal Resistance <sup>(4)</sup> |                 |

| PDIP (θ <sub>JA</sub> )                   | 84.6°C/W        |

| SOIC (θ <sub>JA</sub> )                   | 163.0°C/W       |

| ΤΟ-220 (θ <sub>JA</sub> )                 | 71.2°C/W        |

| PDIP (θ <sub>JC</sub> )                   | 41.2°C/W        |

| SOIC ( $\theta_{JC}$ )                    |                 |

| TO-220 (θ <sub>JC</sub> )                 |                 |

# **Electrical Characteristics**

$T_A = 25^{\circ}C$  with  $4.5V \le V_S \le 18V$ , **bold** values indicate  $-55^{\circ}C \le T_A \le +125^{\circ}C$ , unless noted.

| Symbol          | Parameter                                        | Condition                                                        | Min     | Тур | Max                 | Units    |

|-----------------|--------------------------------------------------|------------------------------------------------------------------|---------|-----|---------------------|----------|

| Power Su        | ipply                                            |                                                                  |         |     |                     |          |

| Vs              | Operating Input Voltage                          |                                                                  | 4.5     |     | 18                  | V        |

| ls              | High Output Quiescent Current                    | V <sub>IN</sub> = 3V (MIC4422A), V <sub>IN</sub> = 0 (MIC4421A)  |         | 0.5 | 1.5<br><b>3</b>     | mA<br>mA |

|                 | Low Output Quiescent Current                     | V <sub>IN</sub> = 0V (MIC4422A), V <sub>IN</sub> = 3V (MIC4421A) |         | 50  | 150<br><b>200</b>   | μΑ<br>μΑ |

| Input           | -                                                |                                                                  |         |     |                     |          |

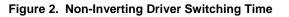

| V <sub>IH</sub> | Logic 1 Input Voltage                            | See Figure 3                                                     | 3.0     | 2.1 |                     | V        |

| V <sub>IL</sub> | Logic 0 Input Voltage                            | See Figure 3                                                     |         | 1.5 | 0.8                 | V        |

| V <sub>IN</sub> | Input Voltage Range                              |                                                                  | -5      |     | V <sub>S</sub> +0.3 | V        |

| l <sub>IN</sub> | Input Current                                    | $0V \le V_{IN} \le V_S$                                          | -10     |     | 10                  | μA       |

| Output          |                                                  |                                                                  |         |     |                     |          |

| V <sub>OH</sub> | High Output Voltage                              | See Figure 1                                                     | Vs+.025 |     |                     | V        |

| V <sub>OL</sub> | Low Output Voltage                               | See Figure 1                                                     |         |     | 0.025               | V        |

| R <sub>0</sub>  | Output Resistance,<br>Output High                | I <sub>OUT</sub> = 10mA, V <sub>S</sub> = 18V                    |         | 0.6 | 1.0<br><b>3.6</b>   | Ω<br>Ω   |

|                 | Output Resistance,<br>Output Low                 | I <sub>OUT</sub> = 10mA, V <sub>S</sub> = 18V                    |         | 0.8 | 1.7<br><b>2.7</b>   | Ω<br>Ω   |

| I <sub>PK</sub> | Peak Output Current                              | V <sub>S</sub> = 18V (See Figure 8)                              |         | 9   |                     | А        |

| I <sub>DC</sub> | Continuous Output Current                        |                                                                  |         | 2   |                     | А        |

| I <sub>R</sub>  | Latch-Up Protection<br>Withstand Reverse Current | Duty Cycle ≤ 2%<br>t ≤ 300µs, <b>Note 5</b>                      | >1500   |     |                     | mA       |

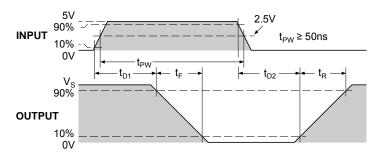

| Switching       | Time (Note 5)                                    |                                                                  |         |     |                     |          |

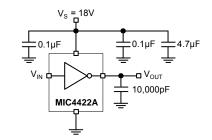

| t <sub>R</sub>  | Rise Time                                        | Test Figure 1, $C_L$ = 10,000pF                                  |         | 20  | 75<br><b>120</b>    | ns<br>ns |

| t <sub>F</sub>  | Fall Time                                        | Test Figure 1, $C_L$ = 10,000pF                                  |         | 24  | 75<br><b>120</b>    | ns<br>ns |

| t <sub>D1</sub> | Delay Time                                       | Test Figure 1                                                    |         | 15  | 68<br><b>80</b>     | ns<br>ns |

| Symbol                            | Parameter                 | Condition                  | Min | Тур | Max             | Units    |

|-----------------------------------|---------------------------|----------------------------|-----|-----|-----------------|----------|

| Switching Time (Note 5) continued |                           |                            |     |     |                 |          |

| t <sub>D2</sub>                   | Delay Time                | Test Figure 1              |     | 35  | 60<br><b>80</b> | ns<br>ns |

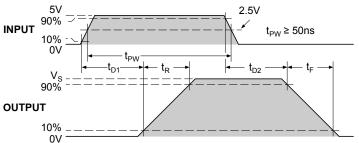

| t <sub>PW</sub>                   | Minimum Input Pulse Width | See Figure 1 and Figure 2. |     | 50  |                 | ns       |

| f <sub>max</sub>                  | Maximum Input Frequency   | See Figure 1 and Figure 2. |     | 1   |                 | MHz      |

Notes:

1. Exceeding the absolute maximum rating may damage the device.

2. The device is not guaranteed to function outside its operating rating.

3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

4. Minimum footprint.

5. Guaranteed by design.

# **Test Circuit**

Figure 1. Inverting Driver Switching Time

# **Control Input Behavior**

Figure 3. Input Hysteresis

t<sub>FALL</sub>

t<sub>RISE</sub>

14 16

18

100k

12

10k

0

1a0

1M

80 120

10M

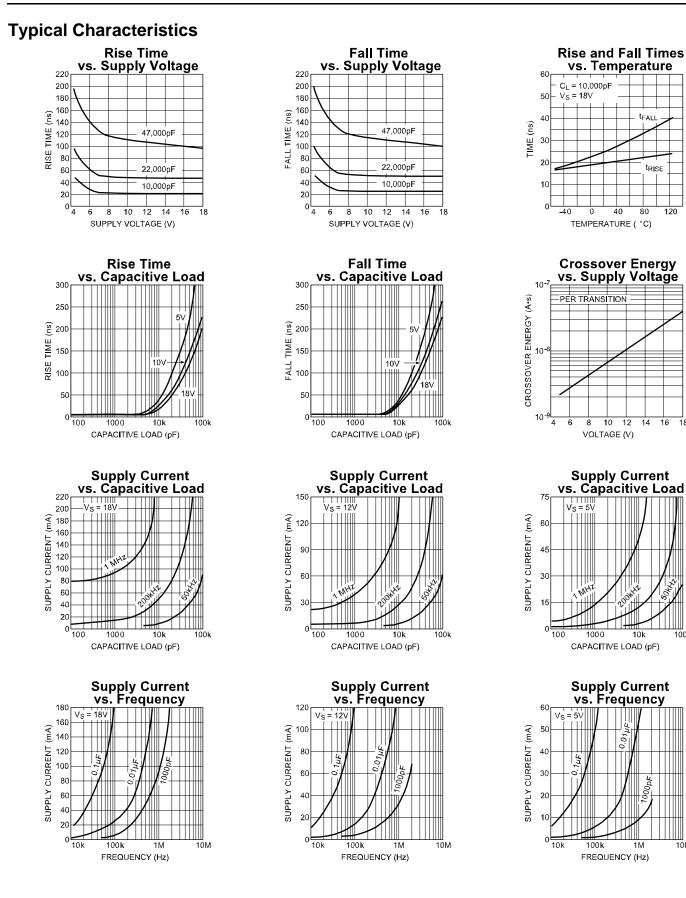

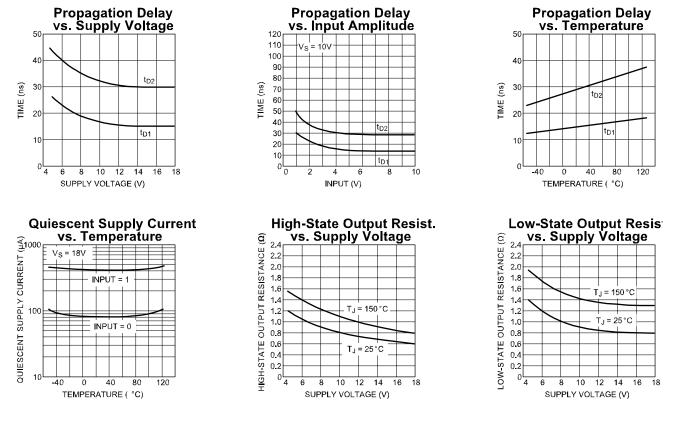

# **Typical Characteristics (continued)**

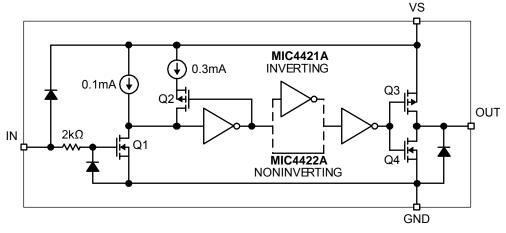

# **Functional Diagram**

Figure 4. MIC4421A/22A Block Diagram

# **Functional Description**

Refer to the functional diagram.

The MIC4422A is a non-inverting driver. A logic high on the IN produces gate drive output. The MIC4421A is an inverting driver. A logic low on the IN produces gate drive output. The output is used to turn on an external Nchannel MOSFET.

#### Supply

$V_{\text{S}}$  (supply) is rated for +4.5V to +18V. External capacitors are recommended to decouple noise.

#### Input

IN (control) is a TTL-compatible input. IN must be forced high or low by an external signal. A floating input will cause unpredictable operation.

A high input turns on Q1, which sinks the output of the 0.1mA and the 0.3mA current source, forcing the input of the first inverter low.

#### Hysteresis

The control threshold voltage, when IN is rising, is slightly higher than the control threshold voltage when CTL is falling.

When IN is low, Q2 is on, which applies the additional 0.3mA current source to Q1. Forcing IN high turns on Q1

which must sink 0.4mA from the two current sources. The higher current through Q1 causes a larger drain-tosource voltage drop across Q1. A slightly higher control voltage is required to pull the input of the first inverter down to its threshold.

Q2 turns off after the first inverter output goes high. This reduces the current through Q1 to 0.1mA. The lower current reduces the drain-to-source voltage drop across Q1. A slightly lower control voltage will pull the input of the first inverter up to its threshold.

#### Drivers

The second (optional) inverter permits the driver to be manufactured in inverting and non-inverting versions.

The last inverter functions as a driver for the output MOSFETs Q3 and Q4.

#### Output

OUT is designed to drive a capacitive load.  $V_{OUT}$  (output voltage) is either approximately the supply voltage or approximately ground, depending on the logic state applied to IN.

If IN is high, and  $V_{S}$  (supply) drops to zero, the output will be floating (unpredictable).

# **Application Information**

#### Supply Bypassing

Charging and discharging large capacitive loads quickly requires large currents. For example, charging a 10,000pF load to 18V in 50ns requires 3.6A.

The MIC4421A/4422A has double bonding on the supply pins, the ground pins and output pins. This reduces parasitic lead inductance. Low inductance enables large currents to be switched rapidly. It also reduces internal ringing that can cause voltage breakdown when the driver is operated at or near the maximum rated voltage.

Internal ringing can also cause output oscillation due to feedback. This feedback is added to the input signal since it is referenced to the same ground.

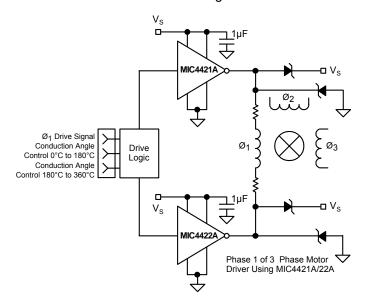

Figure 5. Direct Motor Drive

To guarantee low supply impedance over a wide frequency range, a parallel capacitor combination is recommended for supply bypassing. Low inductance ceramic disk capacitor swith short lead lengths (< 0.5 inch) should be used. A 1 $\mu$ F low ESR film capacitor in parallel with two 0.1 $\mu$ F low ESR ceramic capacitors, (such as AVX RAM Guard<sup>®</sup>), provides adequate bypassing. Connect one ceramic capacitor directly between pins 1 and 4. Connect the second ceramic capacitor directly between pins 8 and 5.

#### Grounding

The high current capability of the MIC4421A/4422A demands careful PC board layout for best performance. Since the MIC4421A is an inverting driver, any ground lead impedance will appear as negative feedback which can degrade switching speed. Feedback is especially noticeable with slow-rise time inputs. The MIC4421A input structure includes about 600mV of hysteresis to ensure clean transitions and freedom from oscillation, but attention to layout is still recommended.

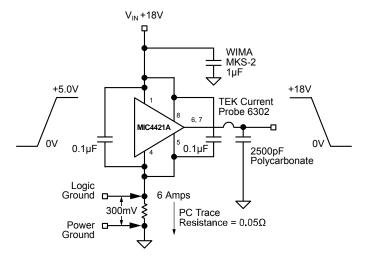

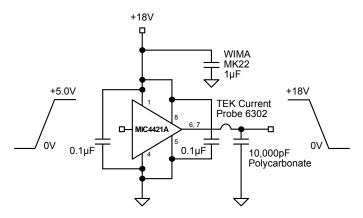

Figure 7 shows the feedback effect in detail. As the MIC4421A input begins to go positive, the output goes negative and several amperes of current flow in the ground lead. As little as  $0.05\Omega$  of PC trace resistance can produce hundreds of millivolts at the MIC4421A ground pins. If the driving logic is referenced to power ground, the effective logic input level is reduced and oscillation may result.

To insure optimum performance, separate ground traces should be provided for the logic and power connections. Connecting the logic ground directly to the MIC4421A GND pins will ensure full logic drive to the input and ensure fast output switching. Both of the MIC4421A GND pins should, however, still be connected to power ground.

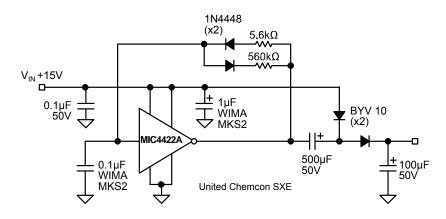

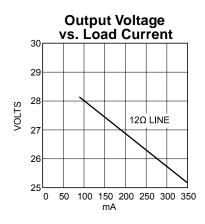

Figure 6. Self Contained Voltage Doubler

#### Input Stage

The input voltage level of the MIC4421A changes the quiescent supply current. The N-Channel MOSFET input stage transistor drives a 320µA current source load. With a logic "1" input, the quiescent supply current is typically 500µA. Logic "0" input level signals reduce quiescent current to 80µA typical.

The MIC4421A/4422A input is designed to provide 600mV of hysteresis. This provides clean transitions, reduces noise sensitivity, and minimizes output stage current spiking when changing states. Input voltage threshold level is approximately 1.5V, making the device TTL compatible over the full temperature and operating supply voltage ranges. Input current is less than  $\pm 10\mu$ A.

The MIC4421A can be directly driven by the TL494, SG1526/1527, SG1524, TSC170, MIC38C42, and similar switch mode power supply integrated circuits. By off loading the power-driving duties to the MIC4421A/ 4422A, the power supply controller can operate at lower dissipation. This can improve performance and reliability.

The input can be greater than the  $V_S$  supply, however, current will flow into the input lead. The input currents can be as high as 30mA p-p (6.4mARMS) with the input. No damage will occur to MIC4421A/4422A however, and it will not latch.

The input appears as a 7pF capacitance and does not change even if the input is driven from an AC source. While the device will operate and no damage will occur up to 25V below the negative rail, input current will increase up to 1mA/V due to the clamping action of the input, ESD diode, and 1k $\Omega$  resistor.

#### **Power Dissipation**

CMOS circuits usually permit the user to ignore power dissipation. Logic families such as 4000 and 74C have outputs which can only supply a few milliamperes of current, and even shorting outputs to ground will not force enough current to destroy the device. The MIC4421A/4422A on the other hand, can source or sink several amperes and drive large capacitive loads at high frequency. The package power dissipation limit can easily be exceeded. Therefore, some attention should be given to power dissipation when driving low impedance loads and/or operating at high frequency.

Figure 7. Switching Time Due to Negative Feedback

The supply current vs. frequency and supply current vs. capacitive load characteristic curves aid in determining power dissipation calculations. Table 1 lists the maximum safe operating frequency for several power supply voltages when driving a 10,000pF load. More accurate power dissipation figures can be obtained by summing the three dissipation sources.

Given the power dissipation in the device, and the thermal resistance of the package, junction operating temperature for any ambient is easy to calculate. For example, the thermal resistance of the 8-pin plastic DIP package, from the data sheet, is 84.6°C/W. In a 25°C ambient, then, using a maximum junction temperature of 150°C, this package will dissipate 1478mW.

Accurate power dissipation numbers can be obtained by summing the three sources of power dissipation in the device:

- Load Power Dissipation (PL)

- Quiescent power dissipation (PQ)

- Transition power dissipation (PT)

Calculation of load power dissipation differs depending on whether the load is capacitive, resistive or inductive.

#### **Resistive Load Power Dissipation**

Dissipation caused by a resistive load can be calculated as:

$$P_L = I^2 R_0 D$$

where:

I = the current drawn by the load

- R<sub>o</sub> = the output resistance of the driver when the output is high, at the power supply voltage used. (See data sheet)

- D = fraction of time the load is conducting (duty cycle).

Table 1. MIC4421A Maximum Operating Frequency

| Vs  | Max Frequency |

|-----|---------------|

| 18V | 220kHz        |

| 15V | 300kHz        |

| 10V | 640kHz        |

| 5V  | 2MHz          |

#### Conditions:

- 1.  $\theta_{JA} = 150^{\circ}C/W$

- 2. T<sub>A</sub> = 25°C

- 3. C<sub>L</sub> = 10,000pF

#### **Capacitive Load Power Dissipation**

Dissipation caused by a capacitive load is simply the energy placed in, or removed from, the load capacitance by the driver. The energy stored in a capacitor is described by the equation:

$E = 1/2 C V^2$

As this energy is lost in the driver each time the load is charged or discharged, for power dissipation calculations the 1/2 is removed. This equation also shows that it is good practice not to place more voltage in the capacitor than is necessary, as dissipation increases as the square of the voltage applied to the capacitor. For a driver with a capacitive load:

$$PL = fC (VS)2$$

where:

f = Operating Frequency

C = Load Capacitance

VS = Driver Supply Voltage

#### Inductive Load Power Dissipation

For inductive loads the situation is more complicated. For the part of the cycle in which the driver is actively forcing current into the inductor, the situation is the same as it is in the resistive case:

$$P_{L1} = I^2 R_0 D$$

However, in this instance the  $R_0$  required may be either the on-resistance of the driver when its output is in the high state, or its on-resistance when the driver is in the low state, depending on how the inductor is connected, and this is still only half the story. For the part of the cycle when the inductor is forcing current through the driver, dissipation is best described as:

$$P_{L2} = I V_D (1 - D)$$

where  $V_D$  is the forward drop of the clamp diode in the driver (generally around 0.7V). The two parts of the load dissipation must be summed in to produce  $P_L$ :

$$P_{L} = P_{L1} + P_{L2}$$

#### **Quiescent Power Dissipation**

Quiescent power dissipation (PQ, as described in the input section) depends on whether the input is high or low. A low input will result in a maximum current drain (per driver) of  $\leq 0.2$ mA; a logic high will result in a current drain of  $\leq 3.0$ mA.

Quiescent power can therefore be found from:

$$P_{Q} = V_{S} [D I_{H} + (1 - D) I_{L}]$$

where:

$I_{H}$  = Quiescent current with input high

I<sub>L</sub> = Quiescent current with input low

D = Fraction of time input is high (duty cycle)

V<sub>S</sub> = Power supply voltage

#### **Transition Power Dissipation**

Transition power is dissipated in the driver each time its output changes state, because during the transition, for a very brief interval, both the N- and P-Channel MOSFETs in the output totem-pole are ON simultaneously, and a current is conducted through them from  $V_S$  to ground. The transition power dissipation is approximately:

$$P_T = 2 f V_S (A \cdot s)$$

where (A•s) is a time-current factor derived from the typical characteristic curve "Crossover Energy vs. Supply Voltage."

Total power (P<sub>D</sub>) then, as previously described is just:

$$P_{D} = P_{L} + P_{Q} + P_{T}$$

#### Definitions

- $C_L$  = Load Capacitance in Farads.

- D = Duty Cycle expressed as the fraction of time the input to the driver is high.

- f = Operating Frequency of the driver in Hertz.

- I<sub>H</sub> = Power supply current drawn by a driver when both inputs are high and neither output is loaded.

- I<sub>L</sub> = Power supply current drawn by a driver when both inputs are low and neither output is loaded.

- $I_D$  = Output current from a driver in Amps.

- P<sub>D</sub> = Total power dissipated in a driver in Watts.

- $P_L$  = Power dissipated in the driver due to the driver's load in Watts.

- $P_Q$  = Power dissipated in a quiescent driver in Watts.

P<sub>T</sub> = Power dissipated in a driver when the output changes states ("shoot-through current") in Watts. NOTE: The "shoot-through" current from a dual transition (once up, once down) for both drivers is stated in Figure 7 in ampere-nanoseconds. This figure must be multiplied by the number of repetitions per second (frequency) to find Watts.

R<sub>o</sub> = Output resistance of a driver in Ohms.

$V_{\rm S}$  = Power supply voltage to the IC in Volts.

Figure 8. Peak Output Current Test Circuit

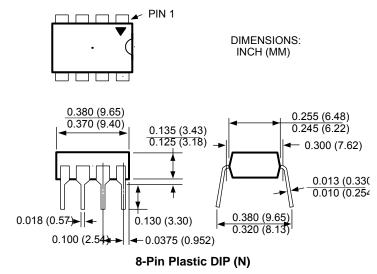

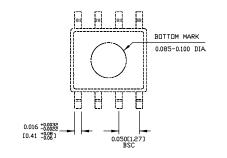

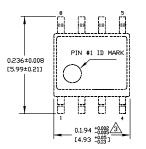

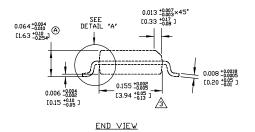

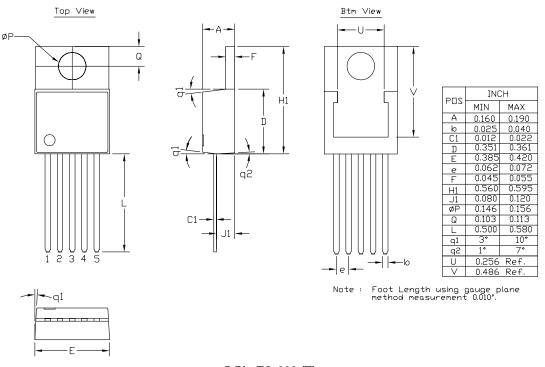

# **Package Information**

BOTTOM VIEW

TOP VIEW

DETAIL "A"

NOTES: 1. DIMENSIONS ARE IN INCHESIMMJ. 2. CONTROLLING DIMENSION: INCHES. 3. DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, EITHER OF WHICH SHALL NOT EXCEED 0.010(0.25) PER SIDE.

8-Pin SOIC (M)

5-Pin TO-220 (T)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2002 Micrel, Incorporated.